(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## WINTER – 2018 EXAMINATION MODEL ANSWER

#### Subject: Digital Techniques & Microprocessor

Subject Code:

22323

### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills).

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q. | Sub  | Answer                                                            | Marking   |

|----|------|-------------------------------------------------------------------|-----------|

| No | Q.N. |                                                                   | Scheme    |

|    |      |                                                                   |           |

| 1. |      | Attempt any <b>FIVE</b> of the following:                         | 10        |

|    | a)   | Draw symbol and write truth table of EX-OR gate.                  | <b>2M</b> |

|    | Ans. | Symbol                                                            |           |

|    |      |                                                                   |           |

|    |      | ALT                                                               |           |

|    |      | B-J)                                                              |           |

|    |      |                                                                   | Symbol    |

|    |      | Truth Table                                                       | <i>1M</i> |

|    |      | Truth Table for two input EX-OR gate. A logical gate whose output |           |

|    |      | is one when odd number of inputs are one, for any other condition |           |

|    |      | output is low.                                                    |           |

|    |      | Inputs Output                                                     |           |

|    |      | A B Y                                                             | Truth     |

|    |      | 0 0 0                                                             | Table     |

|    |      | 1  0  1                                                           | <i>1M</i> |

|    |      | 0 1 1                                                             |           |

|    |      | 1 1 0                                                             |           |

|    |      |                                                                   |           |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code: 22323

| b)        | Define terms "Minterm" and "Maxterm" with proper example of each.                                                                                                                                               | 2M                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| An        | Minterm:         Each individual term in the canonical SOP form is called as Minterm.         Example:         Canonical SOP Y = $ABC + A\overline{BC} + \overline{ABC}$ Each individual term is called minterm | Each<br>Definitio<br>n with<br>example<br>1M |

|           | Maxterm:         Each individual term in the canonical POS form is called as Maxterm.         Example:         Canonical POS $Y = (A + B) \cdot (A + B)$ Each individual term is called maxterm                 | Each<br>Definitio<br>n with<br>example<br>1M |

| c)<br>Ans | Draw symbol of JK flip-flop and write its truth table.<br>Symbol                                                                                                                                                | 2M                                           |

|           | $J \circ \qquad $                                                                        | Symbol<br>1M                                 |

|           | Inputs       Output $J_n$ $K_n$ $Q_{n+1}$ 0       0 $Q_n$ 0       1       0         1       0       1         1       1 $\overline{Q_n}$                                                                        | Truth<br>Table<br>1M                         |

Page 2 / 26

(Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

| <b>d</b> ) | State importance of pipelining in 8086 microprocessor                                                                                   | <i>2M</i> |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Ans.       | • In pipelining, while the current instruction is executing, next                                                                       |           |

|            | instruction is fetched using a queue.                                                                                                   | Any two   |

|            | • Pipelining enables many instructions to be executed at the same                                                                       | points    |

|            | time.                                                                                                                                   | <i>2M</i> |

|            | • It allows execution to be done in fewer cycles.                                                                                       |           |

|            | • Speed up the execution speed of the processor.                                                                                        |           |

|            | • More efficient use of processor.                                                                                                      |           |

| <b>e</b> ) | Give any four applications of digital circuits.                                                                                         | <i>2M</i> |

| Ans.       | Applications of digital circuits                                                                                                        |           |

|            | i) Object Counter                                                                                                                       | Any       |

|            | ii) Dancing Lights                                                                                                                      | relevant  |

|            | iii) Scrolling Notice board                                                                                                             | four      |

|            | iv) Multiplexer                                                                                                                         | applicati |

|            | v) Digital Computers                                                                                                                    | ons       |

|            | vi) Washing machines, Television                                                                                                        | <i>2M</i> |

|            | vii) Digital Calculators                                                                                                                |           |

|            | viii) Military Systems                                                                                                                  |           |

|            | ix) Medical Equipments                                                                                                                  |           |

|            | x) Mobile Phones                                                                                                                        |           |

|            | xi) Radar navigation and guiding systems                                                                                                |           |

|            | xii) Microprocessors                                                                                                                    |           |

| <b>f</b> ) | Define the following terms –                                                                                                            | <i>2M</i> |

|            | (i) Physical Address                                                                                                                    |           |

|            | (ii) Effective Address                                                                                                                  |           |

|            |                                                                                                                                         |           |

| Ans.       | (i) Physical Address<br>(Note: Dimensional)                                                                                             | El.       |

|            | (Note: Diagram is Optional)                                                                                                             | Each      |

|            | Physical: The address given by BIU is 20 bit called as physical<br>address. It is the actual address of the memory location accessed by | definitio |

|            | address. It is the actual address of the memory location accessed by                                                                    | n<br>1M   |

|            | the microprocessor. It is calculated as                                                                                                 | 1 ///     |

|            |                                                                                                                                         |           |

|            |                                                                                                                                         |           |

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code:

22323

|     | (ii) Effective Address<br>Effective Address: Effective address or the offset address is the offset for a memory operand. It is an unassigned 16 bit number that gives the operand's distance in bytes from the beginning of the segment.                                                                                                                        |                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| g)  | Choose instruction for following situations:<br>(i) Addition of 16 bit Hex. No with carry<br>(ii) Division of 8 bit No.<br>(iii) Rotate content of BL by 4 bit.<br>(iv) Perform logical AND operation of AX and BX                                                                                                                                              | 2M                             |

| Ans | <ul> <li>(i) Addition of 16 bit Hex. No with carry</li> <li>(Note any other relevant registers shall also be considered)<br/>ADC Destination 16, Source 16<br/>OR<br/>ADC AX, BX<br/>OR<br/>ADC AX, 4500H</li> <li>(ii) Division of 8 bit No.</li> <li>(Note any other relevant registers shall also be considered)<br/>DIV SOURCE<br/>OR<br/>DIV BL</li> </ul> | Each<br>instructi<br>on<br>½ M |

Subject: Digital Techniques & Microprocessor

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## WINTER – 2018 EXAMINATION MODEL ANSWER

Subject Code: 22323

|    |          | (iii)Rotate content of BL by 4 bit.                                                                                         |          |

|----|----------|-----------------------------------------------------------------------------------------------------------------------------|----------|

|    |          | MOV CL,04H                                                                                                                  |          |

|    |          | ROR BL, CL                                                                                                                  |          |

|    |          | OR                                                                                                                          |          |

|    |          | MOV CL, 04H                                                                                                                 |          |

|    |          | ROL BL, CL                                                                                                                  |          |

|    |          | (iv) Perform logical AND operation of AX and BX<br>AND AX,BX                                                                |          |

| 2. | a)       | Attempt any <u>THREE</u> of the following:<br>Convert following decimal to octal and Hexadecimal                            | 12<br>4M |

|    |          | i) $(297)_{10} = ()_8$                                                                                                      |          |

|    |          | ii) $(453)_{10} = ()_{16}$                                                                                                  | E        |

|    | <b>A</b> |                                                                                                                             | Each     |

|    | Ans.     | (i) $(297)_{10} = ()_8$                                                                                                     | conversi |

|    |          | 8 297                                                                                                                       | on<br>2M |

|    |          |                                                                                                                             | 2M       |

|    |          | 8 37 (LSD)                                                                                                                  |          |

|    |          | 3 7 5 1                                                                                                                     |          |

|    |          | $4 \rightarrow (mso)$                                                                                                       |          |

|    |          |                                                                                                                             |          |

|    |          |                                                                                                                             |          |

|    |          | $(297)_{10} = (451)_8$                                                                                                      |          |

|    |          | $(297)_{10} = (431)_8$                                                                                                      |          |

|    |          | $(ii) (453)_{10} = ()_{16}$                                                                                                 |          |

|    |          | $(453)_{10} = (9)_{16}$ $(453)_{10} = (9)_{16}$ $(453)_{10} = (9)_{16}$ $(Hex)$ $\frac{16}{16} = 5 \longrightarrow 5 (LSD)$ |          |

|    |          |                                                                                                                             |          |

|    |          | 16 (453 (Decimal) (Hex)                                                                                                     |          |

|    |          | $\frac{1628}{1000} 5 \longrightarrow 5 (LSD)$                                                                               |          |

|    |          | $16 1 12 \rightarrow 0 \uparrow$                                                                                            |          |

|    |          |                                                                                                                             |          |

|    |          | 1 (mso)                                                                                                                     |          |

|    |          | $(-453)_{10} = (105)_{16}$                                                                                                  |          |

|    |          |                                                                                                                             |          |

|    |          |                                                                                                                             |          |

|    |          |                                                                                                                             |          |

|    |          |                                                                                                                             |          |

Page 5 / 26

Subject: Digital Techniques & Microprocessor

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject Code: 22323

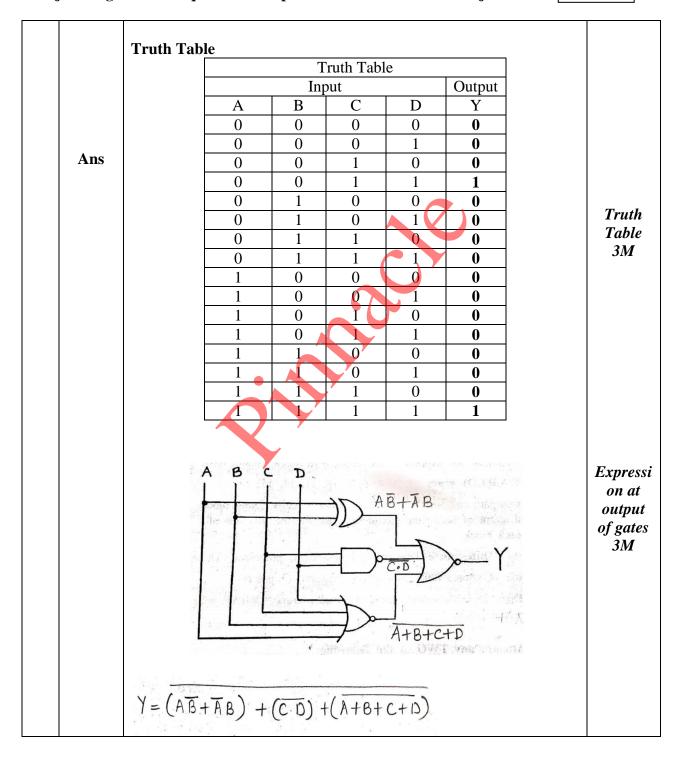

| b)         | Convert the given minterm into standard POS form.<br>$Y(A, B, CD) = (\overline{A}, BC) + (B, \overline{C} \overline{D}) + (\overline{A} \overline{B})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <i>4M</i>                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Ans.       | Note: Solution is given by considering $Y(A, B, CD)$ as $Y(A, B, C, D)$<br>$\begin{array}{l} \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \end{array}{} \\ & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array}{} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \begin{array}{l} & \end{array}{} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array}{} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array}{} \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{l} & \end{array} \\ \begin{array}{l} & \end{array} \\ \end{array}$ | Standar<br>d SOP<br>form<br>2M<br>Conversi<br>on to<br>Standar<br>d POS<br>2M |

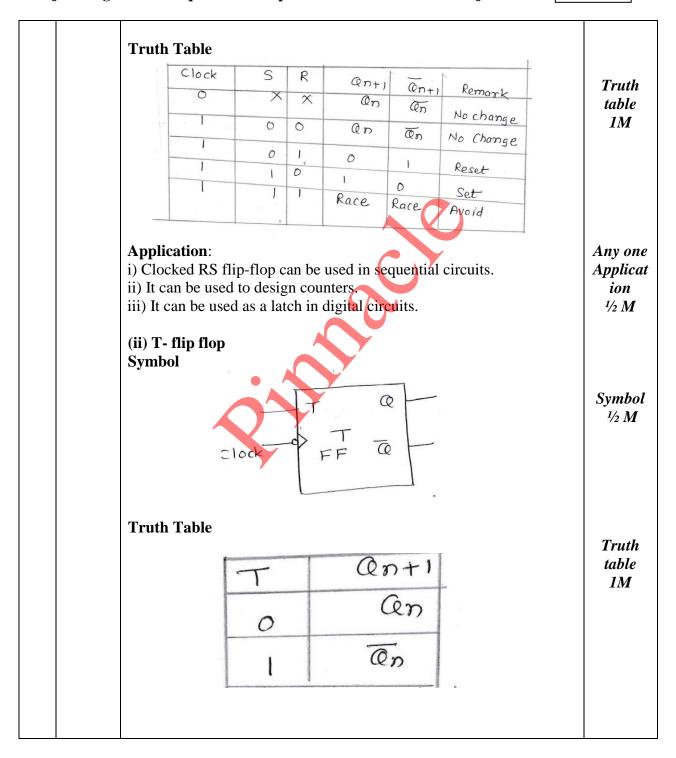

| c)<br>Ans. | Draw symbol and write truth table for the following flip flop and<br>give one application of each.<br>i) Clocked R-S flip flop<br>ii) T- flip flop<br>(i) Clocked R-S flip flop<br>Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>4M</i>                                                                     |

|            | S RS<br>Clock Alip<br>Alop R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol<br>½ M                                                                 |

Page 6 / 26

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code: 22323

|   |            | Application:<br>i) Used to design counters in digital circuits.<br>ii) Can be used in frequency divider circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Any one<br>Applicat<br>ion<br><sup>1</sup> / <sub>2</sub> M |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|   | d)<br>Ans. | <b>Prove</b> $A(\overline{A} + C)(\overline{A}B + C)(\overline{A}BC + \overline{C}) = 0$<br>Note: Any other relevant laws applied shall be considered while obtaining the correct answer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4M                                                          |

|   |            | L'H'S: $= A(\overline{A}+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C))$<br>$= (0+AC)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C))$<br>$= (0+AC)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C))$<br>$= (0+AC)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C))$<br>$= A\overline{A}BC+AC\overline{C}$<br>$= (0+C)(\overline{A}B+C)(\overline{A}B+C)(\overline{A}B+C))$<br>= 0<br>= R + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + S + R + R | Correct<br>solution<br>4M                                   |

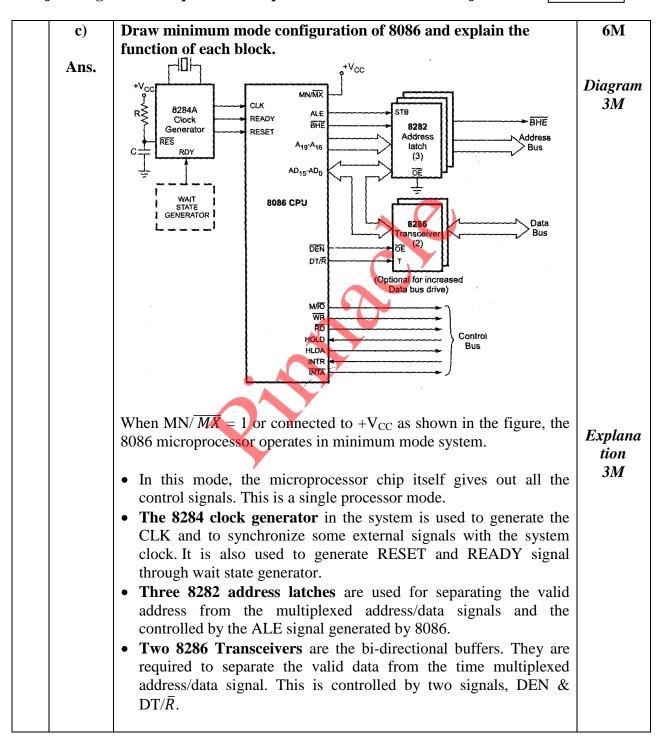

| 3 | a)<br>Ans. | Attempt any <u>THREE</u> of the following:<br>Implement OR gate and NOT gate using "Universal NAND<br>gate". Write expressions for both.<br>1. "OR" gate using "Universal NAND" gate:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>4M                                                    |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output<br>Expressi<br>on<br>1M                              |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Circuit<br>Diagram<br>1M                                    |

Page 8 / 26

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

# WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

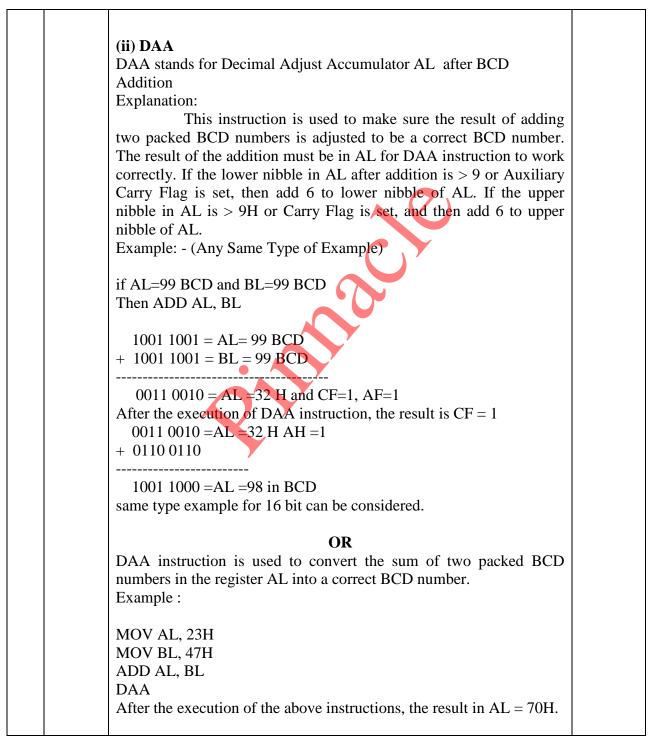

| b)  | 2. "NOT" gate using "Universal NAND" gate:<br>$Y = \overline{A \cdot B} = \overline{A \cdot A} \qquad \dots \text{since } A = B = A$ But $A \cdot A = A$ $\therefore \overline{Y = \overline{A}}$ Input $A = B = A$ $A = B = A$ $A = B = A$ Explain following instructions for 8 bit and 16 bit data.                                                                                                                                                                                                                                                                                                                                                 | Output<br>Expressi<br>on<br>1M<br>Circuit<br>Diagram<br>1M<br>4M                                                             |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|     | (i) PUSH<br>(ii) DAA<br>(iii) IDJV<br>(iv) XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                              |

| Ans | <ul> <li>Note: Any other relevant registers shall also be considered in the example/explanation.</li> <li>(i) PUSH</li> <li>Format: PUSH source</li> <li>This instruction decrements the SP (Stack Pointer) register (by 2) and copies the word specified by source to the location at the top of the stack.</li> <li>Here, Source can be a 16-bit general purpose register, segment register or memory location.</li> <li>Example- PUSH AX</li> <li>OR</li> <li>PUSH AX</li> <li>This instruction decrements the stack pointer by 2 and copies the 16 bit data from AX register to the stack segment where the stack pointer then points.</li> </ul> | Explain<br>ation of<br>each<br><sup>1</sup> / <sub>2</sub> M<br>Example<br>for each<br>case<br><sup>1</sup> / <sub>2</sub> M |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code:

22323

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

| c)<br>Ans. | Draw waves for positive and negative triggering with proper<br>labeling. Identify two situations where these triggering can be<br>used?<br>Note: Any additional relevant point related to triggering situation<br>shall be considered | 4M                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|            | Positive-edge trigger                                                                                                                                                                                                                 | Diagram<br>2M                         |

|            | <ol> <li>Edge triggering can be used in flipflops as clock input.</li> </ol>                                                                                                                                                          | Any<br>relevant<br>situation<br>where |

|            | <ol> <li>It is used in counters circuits.</li> <li>They can be used in shift registers</li> <li>They can be used to synchronous data.</li> </ol>                                                                                      | triggerin<br>g is used<br>2M          |

| d)<br>Ans  | Simplify $Y=F(A, B, CD)$<br>= $\Sigma m$ (1, 2, 8, 9, 10, 12, 13) + d(4,5)<br>Using K-map and write expression<br>Note: Solution is given considering $Y=F(A, B, CD)$ as $Y=F(A, B, C, D)$                                            | 4M                                    |

|            |                                                                                                                                                                                                                                       |                                       |

|            |                                                                                                                                                                                                                                       |                                       |

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

# WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code:

22323

|   |    | • K- map representation for the given expression will be -<br>AB $\begin{array}{c} D & \overline{L}D & \overline{L}$ | Correct<br>K-map<br>2M<br>Correct<br>equation<br>2M |

|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 4 | a) | Attempt any <u>THREE</u> of the following<br>Suggest "Two instruction" for each of the following addressing<br>modes.<br>(i) Register Addressing Mode.<br>(ii) Direct Addressing Mode<br>(iii) Based Indexed Addressing Mode<br>(iv) Immediate Addressing Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>4M                                            |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

### WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code:

22323

| a. MOV AX, CX<br>b. AND AL, BL<br>c. ROR AL, CL<br>ii) <b>Direct addressing mode:</b><br>a.MOV AL, [3000H]<br>b. AND AX,[8000H]<br>c.INC [4712H]<br>iii) <b>Based indexed Addressing mode:</b><br>1.MOV AX, [BX][SI]<br>2.ADD AL, [BX][DI]<br>3.MOV AX, [BX+SI]<br>iv) <b>Immediate addressing mode:</b><br>1.MOV AL, 46H<br>2. MOV BX, 1234H | onside<br>r any<br>two<br>structi<br>on,<br>each<br>structi<br>on<br>½ M |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                               |                                                                          |

| 3. MOV DX, 0040H                                                                                                                                                                                                                                                                                                                              |                                                                          |

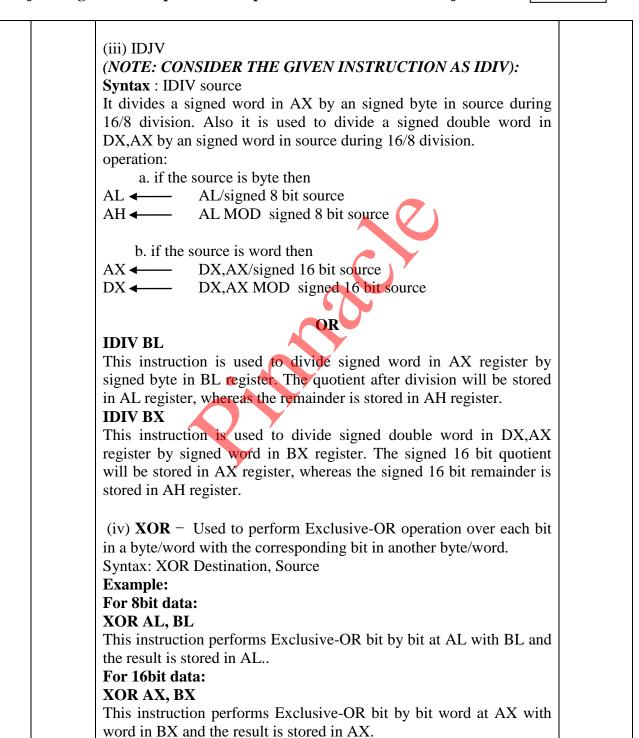

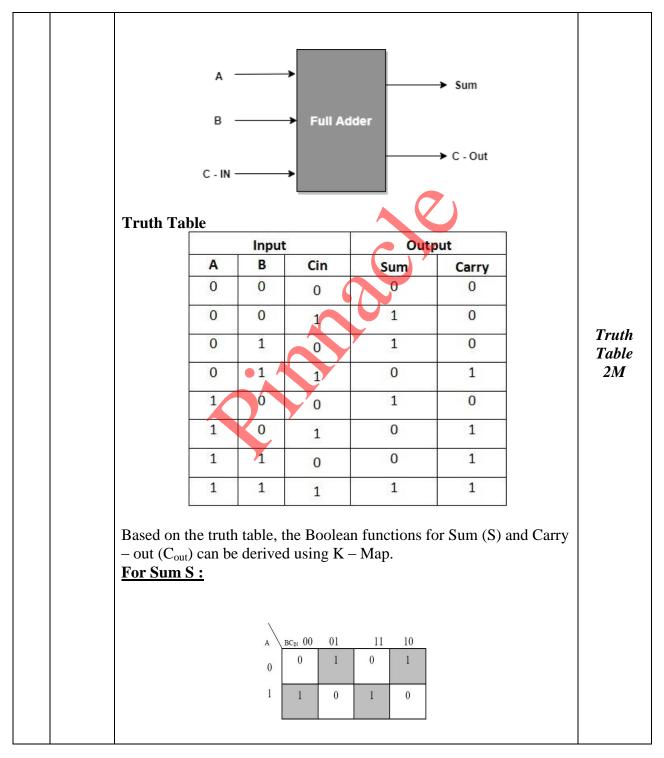

| b) Minimize the expression and draw logic circuit using basic gates. 4                                                                                                                                                                                                                                                                        | <i>4M</i>                                                                |

| <b>F</b> (A,B,CD) = $\pi$ m {0, 2, 4, 6, 7, 10, 11, 14, 15}                                                                                                                                                                                                                                                                                   |                                                                          |

| Ans. Note: Solution is given considering $Y=F(A, B, CD)$ as $Y=F(A, A, CD)$                                                                                                                                                                                                                                                                   |                                                                          |

|                                                                                                                                                                                                                                                                                                                                               |                                                                          |

| K. Map representation for the given expression will be - K-                                                                                                                                                                                                                                                                                   | orrect<br>7-Map<br>2M                                                    |

Page 14 / 26

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## WINTER – 2018 EXAMINATION MODEL ANSWER

Subject: Digital Techniques & Microprocessor

Subject Code:

22323

Page 15 / 26

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

# WINTER – 2018 EXAMINATION **MODEL ANSWER**

Subject: Digital Techniques & Microprocessor

Instruction Set format

Subject Code:

22323

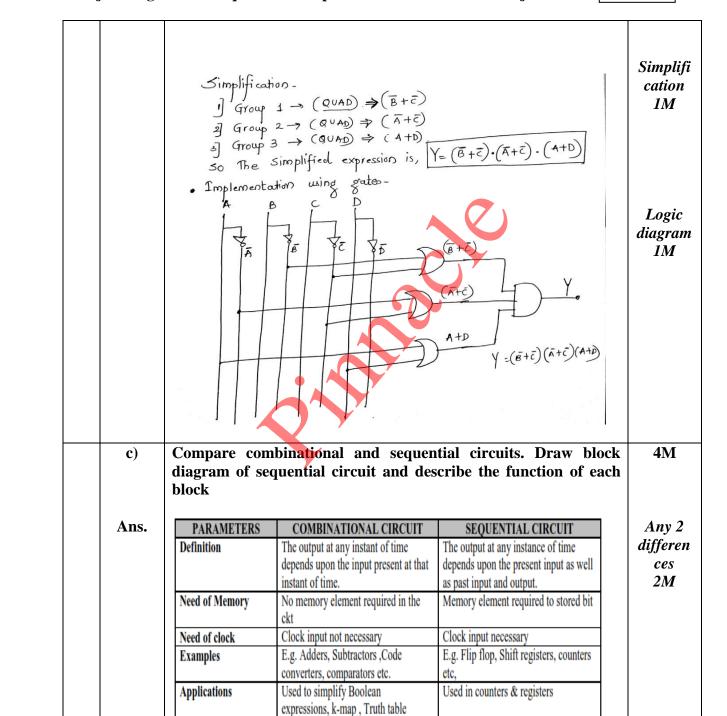

|                                                                                        | Inputs                                                                                                                                   | Combinational<br>logic circuit<br>Memory<br>element                                                                                                                                                            | Output                                                                                                                                                                                                                  | Block<br>diagram<br>1M |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| on th<br>input<br>2. Se<br>feedb<br>3. Se                                              | e present value o<br>signal.<br>quential circuit ca<br>ack circuit.<br>equential circuit                                                 |                                                                                                                                                                                                                |                                                                                                                                                                                                                         | Explana<br>tion<br>1M  |

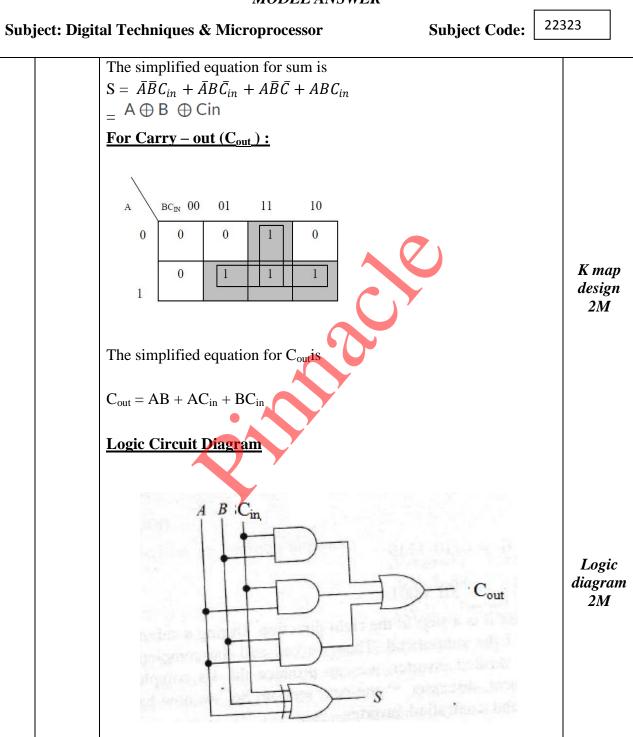

|                                                                                        |                                                                                                                                          | en RISC and CISC pro                                                                                                                                                                                           | ocessor (Three point)                                                                                                                                                                                                   | <b>4</b> M             |

|                                                                                        | ompare 8086 and                                                                                                                          | 80586 (Pentium)(3 po                                                                                                                                                                                           | ints)                                                                                                                                                                                                                   |                        |

|                                                                                        |                                                                                                                                          |                                                                                                                                                                                                                | -                                                                                                                                                                                                                       |                        |

|                                                                                        | ferentiate betwee                                                                                                                        | en RISC and CISC pro                                                                                                                                                                                           | -                                                                                                                                                                                                                       |                        |

| Ans i) Dif<br>Sr.<br>No                                                                | ferentiate betwee<br>PARAMETER                                                                                                           | en RISC and CISC pro<br>RISC<br>PROCESSOPR                                                                                                                                                                     | -                                                                                                                                                                                                                       | Anv                    |

| Sr.                                                                                    |                                                                                                                                          | RISC                                                                                                                                                                                                           | ocessor (Three point)                                                                                                                                                                                                   | Any<br>three           |

| Sr.<br>No                                                                              | PARAMETER                                                                                                                                | RISC<br>PROCESSOPR                                                                                                                                                                                             | cisc processor (Three point)                                                                                                                                                                                            | -                      |

| <b>Sr.</b><br><b>No</b><br>1.                                                          | PARAMETER<br>Instruction set                                                                                                             | RISC<br>PROCESSOPR<br>Few instructions                                                                                                                                                                         | <b>CISC PROCESSOR</b> More instructions                                                                                                                                                                                 | three<br>points        |

| Sr.         No           1.         2.           3.         3.                         | PARAMETER         Instruction set         Data types         Addressing<br>mode                                                          | RISC         PROCESSOPR         Few instructions         Few data types         Few Addressing modes                                                                                                           | Decessor (Three point)CISC PROCESSORMore instructionsMore data typesMore Addressing<br>modes                                                                                                                            | three<br>points        |

| Sr.         No           1.         2.                                                 | PARAMETERInstruction setData typesAddressing                                                                                             | RISC         PROCESSOPR         Few instructions         Few data types         Few Addressing         modes         Large number of                                                                           | Decessor (Three point)CISC PROCESSORMore instructionsMore data typesMore Addressing<br>modesSmall number of                                                                                                             | three<br>points        |